Page 1 of 1

SDRAM new tests

Posted: Sat Dec 26, 2020 6:11 pm

by jotego

I want to share a test for signal integrity that doesn't require special equipment. This test gives some information about signal integrity in the SDRAM. This is a relative test: more is better.

The idea is to have a single core compiled with different SDRAM clock shift settings. Although indeed, the exact delay up to the pin is not well controlled (right now), as a relative measurement, this is reliable. I have made a collection of MRA and RBF files. Each one delays the SDRAM clock by 250ps with respect to the previous one. If you start at a middle value, like 5ns (=5000ps), it should work. As you approach lower and lower delays, it will eventually fail. So will it fail too if you move towards larger delays. The wider the range you get, the better.

These are the values I get for the modules I have.

Code: Select all

Module | Min | Max | Remarks

-------|------|-------|---------

1 | 3.5 | 8.25 |

2 | 2.5 | 8.5 | 32MB

3 | 2.5 | 8.75 | 32MB

4 | 3.0 | 8.0 | 10uF added

7 | 4.0 | 8.25 | min improved to 3.5ns by adding 33uF

8 | 3.5 | 8.0 |

9 | 3.25 | 8.25 |

Module description

ID | Part No | Units | Size

----|------------------|-------|-----

1 | AS4C32M16SB-6T1N | 2 | 128

2 | W9825G6KH-6 | 1 | 32

3 | AS4C16M16SA-6TCN | 1 | 32

4 | AS4C32M16SB-7TCN | 2 | 128

5 | W9825G6KH-6 | 1 | 32

6 | AS4C32M8SA -7TCN | 2 | 64

7 | AS4C32M8SA -7TCN | 4 | 128

8,9 | AS4C32M16SB-6T1N | 2 | 128

Note how module #4 with an extra 10uF electrolytic works better than comparable 128MB modules. #7 also improved when I added extra capacitance.

Please find the files attached. Just unzip them to your MiSTer root folder. This is mainly intended for module builders, but anyone can test their modules at home and check how they do against the ones listed here.

Note that these RBF files only produce analogue video. No HDMI output at all.

Re: SDRAM new tests

Posted: Sun Dec 27, 2020 11:48 am

by terminator2k2

really needed to include HDMI output if you wanted the majority of the community to test this core

Re: SDRAM new tests

Posted: Sun Dec 27, 2020 1:00 pm

by Duffygag

terminator2k2 wrote: ↑Sun Dec 27, 2020 11:48 am

really needed to include HDMI output if you wanted the majority of the community to test this core

Hence why this is mainly intended for module builders

Fan fact Mister community is 50/60% on crt (from polls have that probably won't reflect real life scenarios

)

Thanks as always Jotego, amazing, not a builder per se but I have a couple of modules a solder and parts here, will give it a go as soon as I have some time

Sdram modules is the only thing I didn't make myself as I know even flux can change the way a module respond especially with that pin connector.

Re: SDRAM new tests

Posted: Mon Dec 28, 2020 4:31 pm

by deepthaw

When should I expect to see some type of failure when running these tests?

Re: SDRAM new tests

Posted: Mon Dec 28, 2020 10:46 pm

by Kjeldsen

I ran the tests with the lowest ps and highest ps, it seems that the games, in my case at least, runs just fine no matter what core I choose?

Re: SDRAM new tests

Posted: Wed Dec 30, 2020 10:26 am

by jotego

Just passing the RAM/ROM test at the game boot-up screen is enough. It's surprising that for some people all the files are good. By the way, two people with no-failures for any of these MRA files told me they lived in areas with low population density (and hence less RF noise).

Re: SDRAM new tests

Posted: Wed Dec 30, 2020 10:34 am

by spark2k06

jotego wrote: ↑Wed Dec 30, 2020 10:26 am

By the way, two people with no-failures for any of these MRA files told me they lived in areas with low population density (and hence less RF noise).

How curious, we will have to put the MiSTer in a faraday cage

.

Re: SDRAM new tests

Posted: Wed Dec 30, 2020 3:10 pm

by Kjeldsen

jotego wrote: ↑Wed Dec 30, 2020 10:26 am

Just passing the RAM/ROM test at the game boot-up screen is enough. It's surprising that for some people all the files are good. By the way, two people with no-failures for any of these MRA files told me they lived in areas with low population density (and hence less RF noise).

Thank you. I'm gonna test every one of the files just to be sure.

My home is filled with Philips Hue, Ikea trådløs and plenty of computers. If I could see the radio waves it would be the biggest light show ever

Re: SDRAM new tests

Posted: Wed Dec 30, 2020 4:00 pm

by macro

Lowest and highest also work for me - however, I also get HDMI output from them, which I thought was not present in these cores - so what is happening here ?

Re: SDRAM new tests

Posted: Wed Dec 30, 2020 5:47 pm

by deepthaw

My SDRAM passes all of these tests, and my house is a nightmare of EM interference (smart devices, multiple wifi routers, etc.)

I've never gotten crashes in CPS 1.5 either (other than the unrelated Saturday Night Slammamsters crash) so maybe I have some legitimately good SDRAM?

Re: SDRAM new tests

Posted: Wed Dec 30, 2020 8:05 pm

by Kjeldsen

jotego wrote: ↑Sat Dec 26, 2020 6:11 pm

I want to share a test for signal integrity that doesn't require special equipment. This test gives some information about signal integrity in the SDRAM. This is a relative test: more is better.

The idea is to have a single core compiled with different SDRAM clock shift settings. Although indeed, the exact delay up to the pin is not well controlled (right now), as a relative measurement, this is reliable. I have made a collection of MRA and RBF files. Each one delays the SDRAM clock by 250ps with respect to the previous one. If you start at a middle value, like 5ns (=5000ps), it should work. As you approach lower and lower delays, it will eventually fail. So will it fail too if you move towards larger delays. The wider the range you get, the better.

These are the values I get for the modules I have.

Code: Select all

Module | Min | Max | Remarks

-------|------|-------|---------

1 | 3.5 | 8.25 |

2 | 2.5 | 8.5 | 32MB

3 | 2.5 | 8.75 | 32MB

4 | 3.0 | 8.0 | 10uF added

7 | 4.0 | 8.25 | min improved to 3.5ns by adding 33uF

8 | 3.5 | 8.0 |

9 | 3.25 | 8.25 |

Module description

ID | Part No | Units | Size

----|------------------|-------|-----

1 | AS4C32M16SB-6T1N | 2 | 128

2 | W9825G6KH-6 | 1 | 32

3 | AS4C16M16SA-6TCN | 1 | 32

4 | AS4C32M16SB-7TCN | 2 | 128

5 | W9825G6KH-6 | 1 | 32

6 | AS4C32M8SA -7TCN | 2 | 64

7 | AS4C32M8SA -7TCN | 4 | 128

8,9 | AS4C32M16SB-6T1N | 2 | 128

Note how module #4 with an extra 10uF electrolytic works better than comparable 128MB modules. #7 also improved when I added extra capacitance.

Please find the files attached. Just unzip them to your MiSTer root folder. This is mainly intended for module builders, but anyone can test their modules at home and check how they do against the ones listed here.

Note that these RBF files only produce analogue video. No HDMI output at all.

I did a retest just to be sure.

I loaded every core in the test package and the game loaded to the title screen with them all.

If you want me to test anything else just let me know.

Re: SDRAM new tests

Posted: Sat Jan 02, 2021 8:01 pm

by Overkill

Lowest and highest also work for me - however, I also get HDMI output from them, which I thought was not present in these cores - so what is happening here ?

HDMI output works, but in direct video mode (low res in Contra), so people using lcd monitor which don't accept 240p on hdmi will give black screen.

I was able to run all the cores perfectly on two MiSTer units, both with Ricardo's UltimateMiSTer shop "XS-D 128MB SDRAM Memory". One from the first batch, and the other bought recently.

But I didn't found any error before on the CPS 1.5 Cores at 96MHz also, so I'm lucky

Re: SDRAM new tests

Posted: Thu Jan 07, 2021 1:55 am

by rhester72

Bought mine off eBay:

https://www.ebay.com/itm/Mister-FPGA-SD ... 2749.l2649

It passes every test.

My house has 69 (2.4GHz and 5GHz) wireless devices active, so I wouldn't exactly call it low-RF. =)

More data:

- I *don't* have the I/O or USB expansion boards, just a bare DE-10 Nano with the 128MB module as above

- My board is housed with a Noctua fan in this case:

https://corei64.com/shop/index.php?rout ... rch=mister

- I have a Microsoft wireless (2.4GHz) keyboard, a USB-based 5GHz WiFi adapter, and a wired controller connected to an unpowered USB hub

Re: SDRAM new tests

Posted: Sun Jan 17, 2021 12:27 pm

by d18c7db

jotego wrote: ↑Wed Dec 30, 2020 10:26 am

It's surprising that for some people all the files are good.

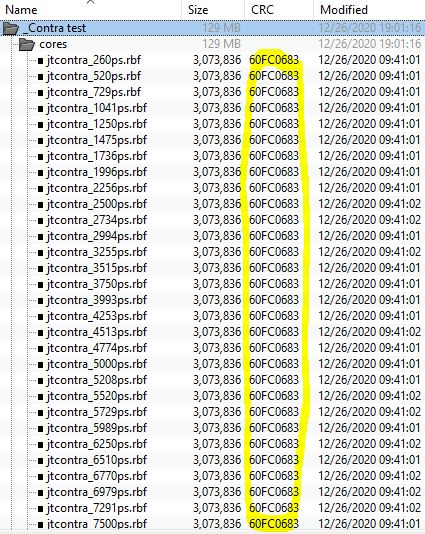

Uhmm... I think all the tests are invalid based on the fact that in the file "Contra test.7z" all the .rbf files with different time offsets are in fact

identical at the binary level (same checksums) and the .mra files don't seem to pass any timing offset parameters to them, they just select one of the many identical .rbf files.

In other words, it doesn't matter what time delay you choose, you're running the same test.

- CHKSUMS.JPG (107.3 KiB) Viewed 5114 times